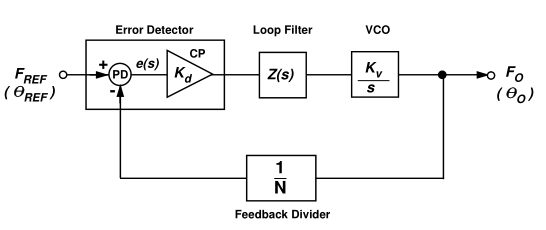

核心结构是

PD(Phase Detector)+LPF(Low-Pass Filter)+VCO(Voltage Controlled Oscillator)+FD(Feedback Divider)

1. The phase detector (PD) and charge pump (CP).

2. The loop filter, with a transfer function of Z(s)

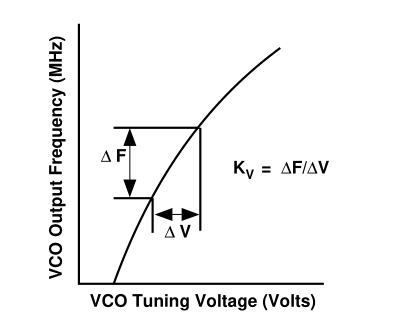

3. The voltage-controlled oscillator (VCO), with a sensitivity of Kv/s

4. The feedback divider, 1/N

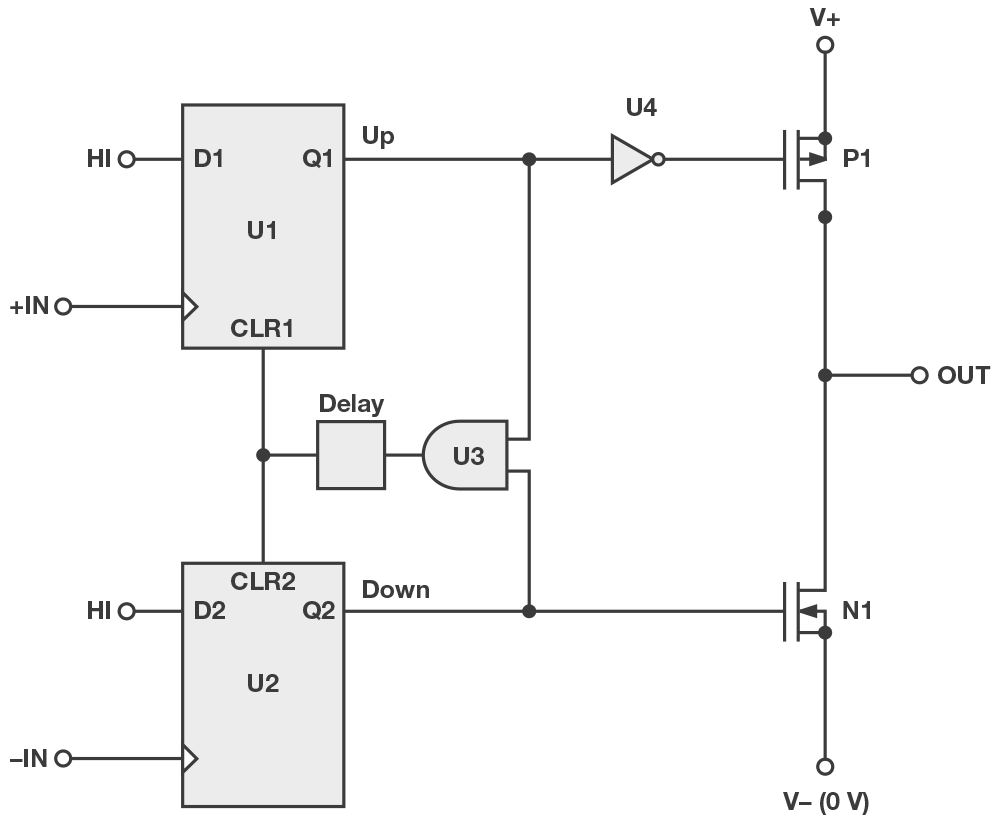

鉴频鉴相器

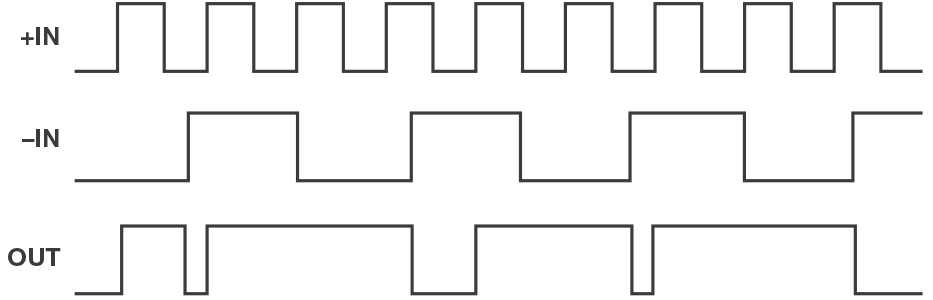

鉴频鉴相器将+IN端的FREF输入与和-IN端的反馈信号进行比较。使用两个D型触发器和一个延迟元件。一路Q输出使能正电流源,另一路Q输出使能负电流源。给目标电荷泵充放电。

如果+IN端的输入频率高于-IN端;或者说+IN信号正边沿,比-IN信号提前到达,会输出高。既打开连接于后级的电荷泵电容充电回路,其在PLL低通滤波器中积分后,会使VCO调谐电压上升。如此,-IN频率将随著VCO频率的提高而提高,如果-IN频率高于+IN频率,则发生相反的情况。两个PFD输入最终会收敛或锁定到相同频率。

之后,由PLL的参考和PFD电路贡献的所有频内杂波都被低通滤波器滤除,只在回路路频带宽外留下低得多的VCO杂波。当输出频率等于输入频率时,PLL配置最简单。这种PLL称为时钟净化PLL。对于此类时钟净化应用,一般使用窄频宽(<1kHz)低通滤波器。

高频整数N分频架构

为了产生一系列更高频率,应使用VCO,其调谐范围比VCO更宽。这常用于跳频或扩频跳频(FHSS)应用中。在这种PLL中,输出是参考频率的很多倍。压控振荡器含有可变调谐元件,例如变容二极管,其电容随输入电压而改变,形成一个可调谐振电路,从而可以产生一系列频率。PLL可以被认为是该VCO的控制系统。

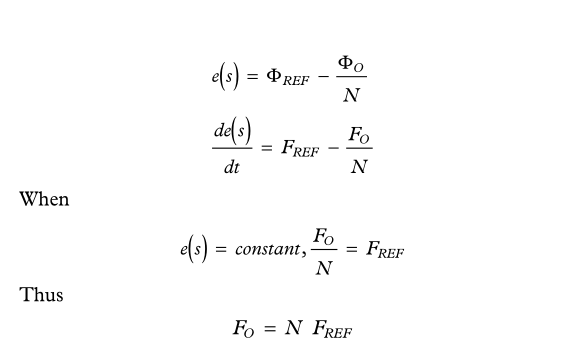

反馈分频器用于将VCO频率分频为PD频率,从而允许PLL生成PD频率倍数的输出频率。分频器也可以用在参考路径中,这样就可以使用比PFD频率更高的参考频率。

![]()

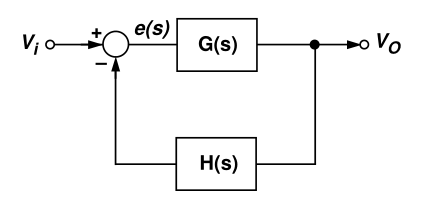

The loop filter is a low-pass type, typically with one pole and one zero. The transient response of the loop depends on:

1. the magnitude of the pole/zero,

2. the charge pump magnitude,

3. the VCO sensitivity,

4. the feedback factor, N.